# Sil9687A Port Processor

Document # SiI-DS-1140-A

December 2012

#### **Copyright Notice**

Copyright © 2011-2012 Silicon Image, Inc. All rights reserved. The contents of these materials contain proprietary and confidential information (including trade secrets, copyright, and other Intellectual Property interests) of Silicon Image, Inc. or its affiliates. All rights are reserved and contents, (in whole or in part) may not be reproduced, downloaded, disseminated, published, or transferred in any form or by any means, except with the prior written permission of Silicon Image, Inc. or its affiliates. You may not use these materials except only for your bona fide non-commercial evaluation of your potential purchase of products and/or services from Silicon Image or its affiliates; and only in connection with your purchase of products or services from Silicon Image or its affiliates, and only in accordance with the terms and conditions stipulated. Copyright infringement is a violation of federal law subject to criminal and civil penalties. You have no right to copy, modify, transfer, sublicense, publicly display, create derivative works of, distribute these materials, or otherwise make these materials available, in whole or in part, to any third party.

#### **Patents**

The subject matter described herein may contain one or more inventions claimed in patents or patents pending owned by Silicon Image, Inc. or its affiliates.

#### Trademark Acknowledgment

Silicon Image<sup>®</sup>, the Silicon Image logo, SteelVine<sup>®</sup>, Simplay<sup>®</sup>, Simplay HD<sup>®</sup>, the Simplay HD logo, Satalink<sup>®</sup>, InstaPort<sup>®</sup>, the InstaPort Logo, InstaPrevue<sup>TM</sup>, and TMDS<sup>®</sup> are trademarks or registered trademarks of Silicon Image, Inc. in the United States or other countries. HDMI<sup>®</sup> and the HDMI logo with High-Definition Multimedia Interface are trademarks or registered trademarks of, and are used under license from, HDMI Licensing, LLC. in the United States or other countries. MHL<sup>®</sup> and the MHL Logo are trademarks or registered trademarks of, and are used under license from, MHL, LLC. in the United States or other countries. All other trademarks and registered trademarks are the property of their respective owners in the United States or other countries. The absence of a trademark symbol does not constitute a waiver of Silicon Image's trademark or other intellectual property rights with regard to a product name, logo or slogan.

#### **Export Controlled Document**

This document contains information subject to the Export Administration Regulations (EAR) and has a classification of EAR99 or is controlled for Anti-Terrorism (AT) purposes. Transfer of this information by any means to an EAR Country Group E:1 or foreign national thereof (whether in the U.S. or abroad) may require an export license or other approval from the U.S. Department of Commerce, For more information, contact the Silicon Image Director of Global Trade Compliance.

#### **Further Information**

To request other materials, documentation, and information, contact your local Silicon Image, Inc. sales office or visit the Silicon Image, Inc. web site at www.siliconimage.com.

#### **Revision History**

| Revision | Date       | Comment                   |

|----------|------------|---------------------------|

| A        | 12/10/2012 | First production release. |

© 2011-2012 Silicon Image, Inc. All rights reserved.

# **Table of Contents**

| General Description                                                                                                                                                                                                                                                                                                             |          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| HDMI Inputs and Output                                                                                                                                                                                                                                                                                                          |          |

| Performance Improvement Features                                                                                                                                                                                                                                                                                                |          |

| Control Capability                                                                                                                                                                                                                                                                                                              | 1        |

| Packaging                                                                                                                                                                                                                                                                                                                       | 1        |

| Pin Diagram                                                                                                                                                                                                                                                                                                                     | 2        |

| Functional Description                                                                                                                                                                                                                                                                                                          |          |

| Always-on Section                                                                                                                                                                                                                                                                                                               | 4        |

| Serial Ports Block                                                                                                                                                                                                                                                                                                              | 4        |

| Static RAM Block                                                                                                                                                                                                                                                                                                                | 4        |

| NVRAM Block                                                                                                                                                                                                                                                                                                                     | 4        |

| HDCP Register Block                                                                                                                                                                                                                                                                                                             | 4        |

| OTP ROM Block                                                                                                                                                                                                                                                                                                                   | 4        |

| Booting Sequencer                                                                                                                                                                                                                                                                                                               | 5        |

| Configuration, Status, and Interrupt Control Registers Block                                                                                                                                                                                                                                                                    | 5        |

| Configuration, Status, and Interrupt Control Registers Block  MHL Control Block  Power-down Section                                                                                                                                                                                                                             | 5        |

| Power-down Section                                                                                                                                                                                                                                                                                                              | 5        |

| TMDS Receiver Blocks                                                                                                                                                                                                                                                                                                            | 5        |

| Power-down Section                                                                                                                                                                                                                                                                                                              | 5        |

| MHL Demultiplexer Blocks                                                                                                                                                                                                                                                                                                        | 5        |

| 2:1 HDMI/MHL Multiplexer Blocks                                                                                                                                                                                                                                                                                                 | 5        |

| Packet Analyzer Blocks                                                                                                                                                                                                                                                                                                          | 5        |

| HDCP Authentication Block                                                                                                                                                                                                                                                                                                       | 5        |

| MP and RP HDMI Receive Data Path and HDCP Unmask Blocks                                                                                                                                                                                                                                                                         | <i>6</i> |

| InstaPrevue Block                                                                                                                                                                                                                                                                                                               | <i>6</i> |

| AV Mute Block                                                                                                                                                                                                                                                                                                                   | <i>6</i> |

| TMDS Transmitter Block                                                                                                                                                                                                                                                                                                          | 6        |

| ARC Block                                                                                                                                                                                                                                                                                                                       | 6        |

| MP and RP HDMI Receive Data Path and HDCP Unmask Blocks InstaPrevue Block AV Mute Block TMDS Transmitter Block ARC Block Electrical Specifications Absolute Maximum Conditions Normal Operating Conditions DC Specifications AC Specifications Miscellaneous Timing *Note: This time is required due to internal Power-on Reset |          |

| Absolute Maximum Conditions                                                                                                                                                                                                                                                                                                     |          |

| Normal Operating Conditions.                                                                                                                                                                                                                                                                                                    | 8        |

| DC Specifications                                                                                                                                                                                                                                                                                                               | 9        |

| AC Specifications                                                                                                                                                                                                                                                                                                               | 11       |

| Miscellaneous Timing                                                                                                                                                                                                                                                                                                            | 12       |

|                                                                                                                                                                                                                                                                                                                                 |          |

| Reset Timings Pin Descriptions                                                                                                                                                                                                                                                                                                  | 12       |

| Pin Descriptions.                                                                                                                                                                                                                                                                                                               | 13       |

| HDMI and MHL Receiver Port Pins                                                                                                                                                                                                                                                                                                 | 13       |

| Audio Pins                                                                                                                                                                                                                                                                                                                      |          |

| HDMI Transmitter Port Pins                                                                                                                                                                                                                                                                                                      |          |

| System Switching Pins                                                                                                                                                                                                                                                                                                           | 14       |

| Control Pins                                                                                                                                                                                                                                                                                                                    |          |

| Configuration Pins                                                                                                                                                                                                                                                                                                              |          |

| Power and Ground Pins                                                                                                                                                                                                                                                                                                           |          |

| Reserved Pins                                                                                                                                                                                                                                                                                                                   | 16       |

| Unused Pins                                                                                                                                                                                                                                                                                                                     | 16       |

| Feature Information                                                                                                                                                                                                                                                                                                             |          |

| Standby and HDMI Port Power Supplies                                                                                                                                                                                                                                                                                            |          |

| Hardware Reset.                                                                                                                                                                                                                                                                                                                 |          |

| Built-in Pattern Generator.                                                                                                                                                                                                                                                                                                     |          |

| 3D Video Formats                                                                                                                                                                                                                                                                                                                |          |

| InstaPrevue Format Support                                                                                                                                                                                                                                                                                                      |          |

| Input Video Resolution Detection and InfoFrame Extraction                                                                                                                                                                                                                                                                       |          |

| MHL PackedPixel Mode                                                                                                                                                                                                                                                                                                            |          |

| Audio Return Channel                                                                                                                                                                                                                                                                                                            |          |

| 1 10010 1000111 Chamber                                                                                                                                                                                                                                                                                                         |          |

| EDID M                                 | 22 |

|----------------------------------------|----|

| EDID Memory                            | 23 |

| EDID MemoryLocal I <sup>2</sup> C Port | 24 |

| Design Recommendations                 | 25 |

| Audio Return Channel Design            | 25 |

| MHL Power and Cable Detect Design      | 25 |

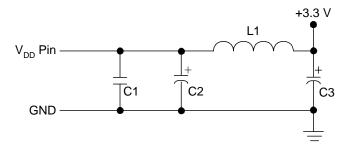

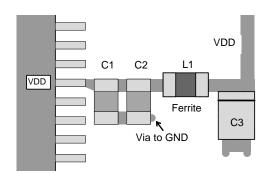

| Power Supply Decoupling                | 26 |

| Power Supply Sequencing                | 27 |

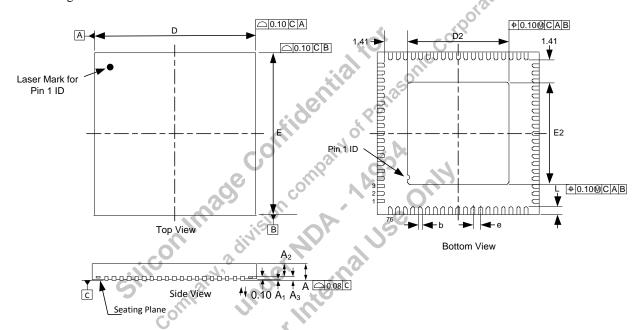

| Package Information                    | 28 |

| ePad Requirements                      | 28 |

| Package Dimensions                     | 28 |

| Package Dimensions                     | 29 |

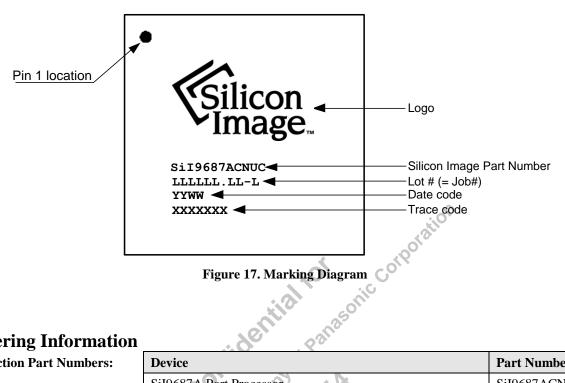

| Ordering Information                   | 29 |

| Ordering Information                   | 30 |

| Standards Documents                    |    |

| Silicon Image Documents                |    |

|                                        |    |

# **List of Figures**

| Figure 1. Port Processor Application                                                                                                                                                                       |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2. Pin Diagram (Top View)                                                                                                                                                                           |    |

| Figure 3. Functional Block Diagram                                                                                                                                                                         |    |

| Figure 4. I <sup>2</sup> C Control Mode Configuration                                                                                                                                                      | 4  |

| Figure 5. Test Point VDDTP for VDD Noise Tolerance Spec                                                                                                                                                    | 8  |

| Figure 6. Test Point SBVCC5TP for SBVCC5 Measurement                                                                                                                                                       | 8  |

| Figure 7. RESET_N Minimum Timing                                                                                                                                                                           | 12 |

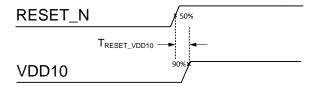

| Figure 8. RESET_N to VDD10 Timing                                                                                                                                                                          |    |

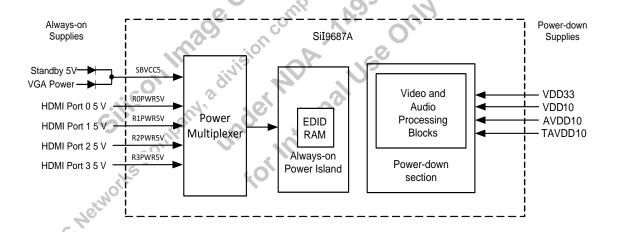

| Figure 9. Standby Power Supply Diagram                                                                                                                                                                     | 17 |

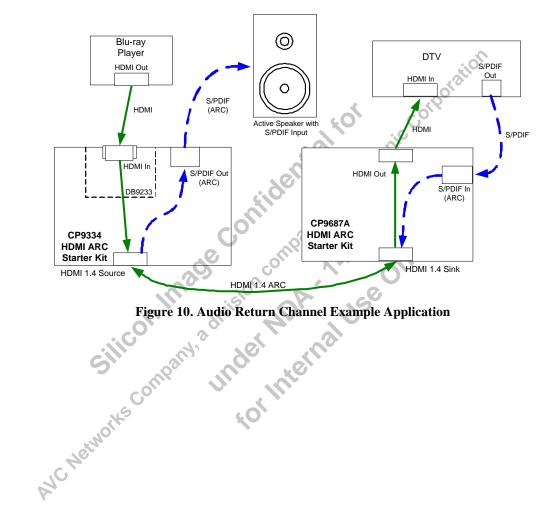

| Figure 10. Audio Return Channel Example Application                                                                                                                                                        |    |

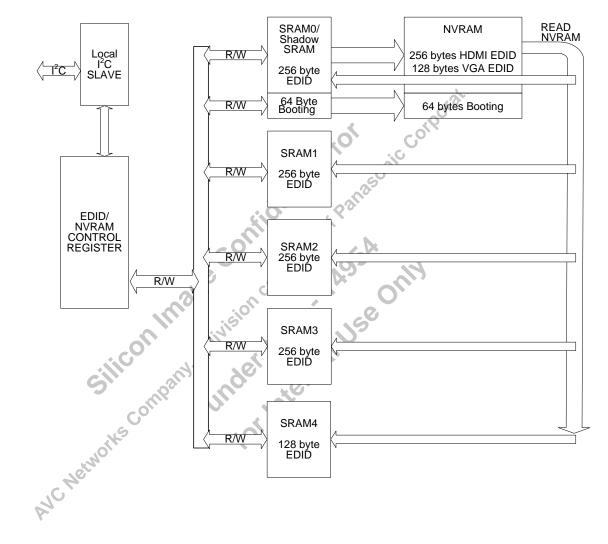

| Figure 11. EDID Block Diagram                                                                                                                                                                              |    |

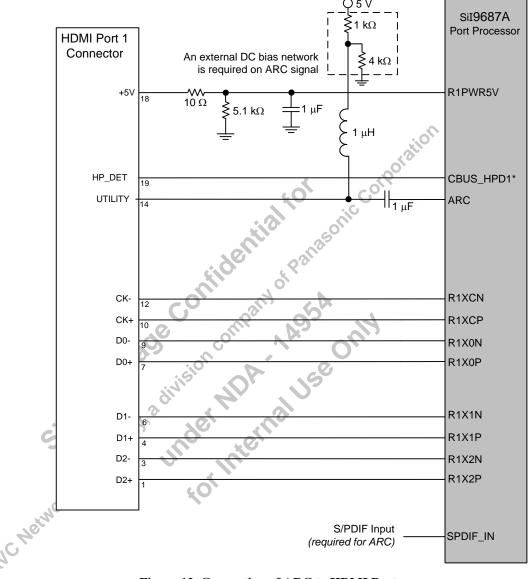

| Figure 12. Connection of ARC to HDMI Port                                                                                                                                                                  |    |

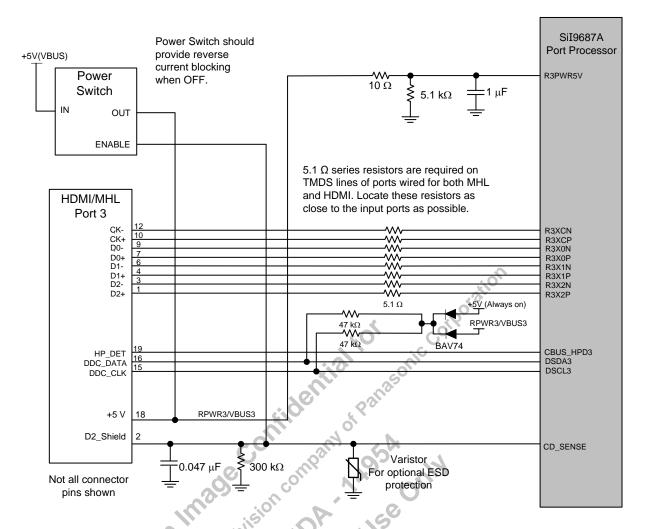

| Figure 13. Connection of MHL and HDMI Combined Port                                                                                                                                                        |    |

| Figure 14. Decoupling and Bypass Schematic                                                                                                                                                                 |    |

| Figure 15. Decoupling and Bypass Capacitor Placement                                                                                                                                                       | 27 |

| Figure 16. Package Diagram                                                                                                                                                                                 | 28 |

| Ciarra 17 Martina Diagram                                                                                                                                                                                  | 29 |

| List of Tables                                                                                                                                                                                             |    |

| Table 1. Absolute Maximum Conditions                                                                                                                                                                       | 7  |

| Table 2. ESD Specifications                                                                                                                                                                                | 7  |

| Table 2 Normal Operating Conditions                                                                                                                                                                        | O  |

| Table 4. Digital I/O Specifications  Table 5. Power Requirements  Table 6. TMDS Input DC Specifications—HDMI Mode  Table 7. TMDS Input DC Specifications—MHL Mode.  Table 8. TMDS Output DC Specifications | 9  |

| Table 5. Power Requirements                                                                                                                                                                                | 9  |

| Table 6. TMDS Input DC Specifications—HDMI Mode                                                                                                                                                            | 10 |

| Table 7. TMDS Input DC Specifications—MHL Mode                                                                                                                                                             | 10 |

| Table 8. TMDS Output DC Specifications                                                                                                                                                                     | 10 |

| Table 9. Single Mode Audio Return Channel DC Specifications                                                                                                                                                | 10 |

| Table 10. CBUS DC Specifications                                                                                                                                                                           |    |

| Table 11. TMDS Input Timing AC Specifications – HDMI Mode                                                                                                                                                  |    |

| Table 12. TMDS Input Timing AC Specifications – MHL Mode                                                                                                                                                   |    |

| Table 13. TMDS Output Timing AC Specifications                                                                                                                                                             |    |

| Table 14. Single Mode Audio Return Channel AC Specifications                                                                                                                                               |    |

| Table 15. S/PDIF Input Port AC Specifications                                                                                                                                                              |    |

| Table 16. CBUS AC Specifications                                                                                                                                                                           | 12 |

| Table 17. I <sup>2</sup> C Timing                                                                                                                                                                          |    |

| Table 18. Miscellaneous Timing                                                                                                                                                                             |    |

| Table 19. Required Connection for Unused Pins                                                                                                                                                              |    |

| Table 20. Description of Power Modes                                                                                                                                                                       |    |

| Table 21. Built-in Pattern List                                                                                                                                                                            |    |

| Table 22. Supported HDMI 3D Video Formats                                                                                                                                                                  |    |

| Table 23. Supported MHL 3D Video Formats                                                                                                                                                                   |    |

| Table 24. InstaPrevue Supported Formats                                                                                                                                                                    |    |

| Table 25. I <sup>2</sup> C Register Address Groups                                                                                                                                                         |    |

| Table 26. Referenced Documents                                                                                                                                                                             |    |

| Table 27. Standards Groups Contact Information                                                                                                                                                             |    |

| Table 28 Silicon Image Dublications                                                                                                                                                                        | 30 |

# **General Description**

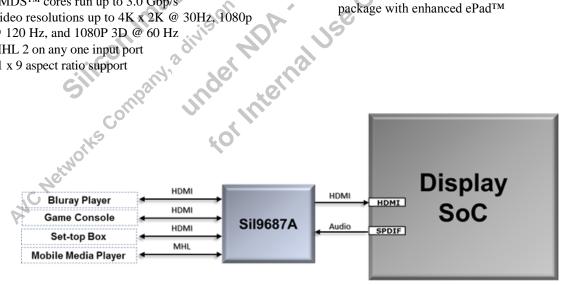

The SiI9687A HDMI port processor delivers four HDMI inputs with fast InstaPort<sup>TM</sup> S port switching to DTVs and other consumer electronic devices. One HDMI input can automatically detect and switch between HDMI and Mobile High-definition Link (MHL<sup>TM</sup>) mode. The SiI9687A also supports InstaPrevue<sup>TM</sup>, which provides real-time previews of the HDMI/DVI/MHL input ports overlaid on top of the selected main video.

The SiI9687A device supports the MHL 2 Specification on any one input port. The port processor features all MHL 2 required and conditional 3D video modes including 1920 x 1080p 24 Hz 3D Frame Sequential, It supports the UTF-8 character protocol subcommands. The SiI9687A device supports HDMI frequencies up to 300 MHz, which enables 4K x 2K @ 30 Hz and 1080p 3D @ 60 Hz.

The port processor supports the Audio Return Channel (ARC) described in the HDMI 1.4b Specification, which transmits an S/PDIF audio signal from an HDMI sink to an HDMI source in the opposite direction of the TMDS data flow. ARC simplifies audio connectivity and switching for the consumer.

#### **HDMI Inputs and Output**

- Four HDMI input ports and one output port

- HDMI, HDCP, and DVI compatibility

- TMDS<sup>TM</sup> cores run up to 3.0 Gbp/s

- Video resolutions up to 4K x 2K @ 30Hz, 1080p @ 120 Hz, and 1080P 3D @ 60 Hz

- MHL 2 on any one input port

- 21 x 9 aspect ratio support

- Pre-programmed with HDCP keys

- Single mode ARC

#### **Performance Improvement Features**

- InstaPrevue technology adds a preview image of the background ports to the video of the main port

- InstaPort™ S viewing technology allows HDMI input port switching in about one second

- Adaptive equalizer provides long cable support

- Built-in pattern generator to speed design, test, and manufacturing

- AVI, Audio InfoFrame, and video input resolution detection for all input ports, accessible port-by-port

- Hardware-based HDCP error detection and recovery minimizes firmware intervention

- Automatic output mute and unmute based on link stability, such as cable connect/detach

#### **Control Capability**

- Integrated EDID and DDC support for the HDMI/VGA ports using a 512-byte NVRAM shared between ports that loads into separate 256-byte SRAM for each of four HDMI ports and 128-byte SRAM for VGA EDID

- Individual control of Hot Plug Detect (HPD) for

- Controllable by the local I<sup>2</sup>C bus

# **Packaging**

76-pin, 9 mm x 9 mm, 0.4 mm pitch MQFN package with enhanced ePad<sup>TM</sup>

**Figure 1. Port Processor Application**

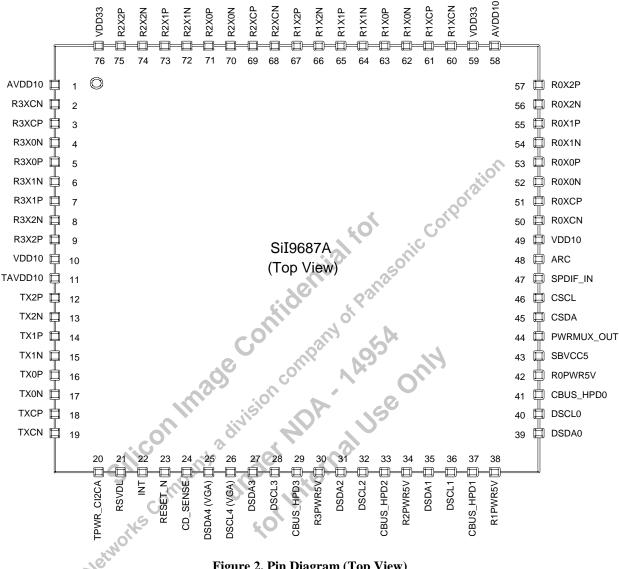

#### Pin Diagram

Figure 2 shows the pin assignments of the SiI9687A port processor. A description of the pin functions is in the Pin Descriptions section beginning on page 13. The package is a 9 mm x 9 mm 76-pin MQFN with an ePad, which *must* be connected to ground.

Figure 2. Pin Diagram (Top View)

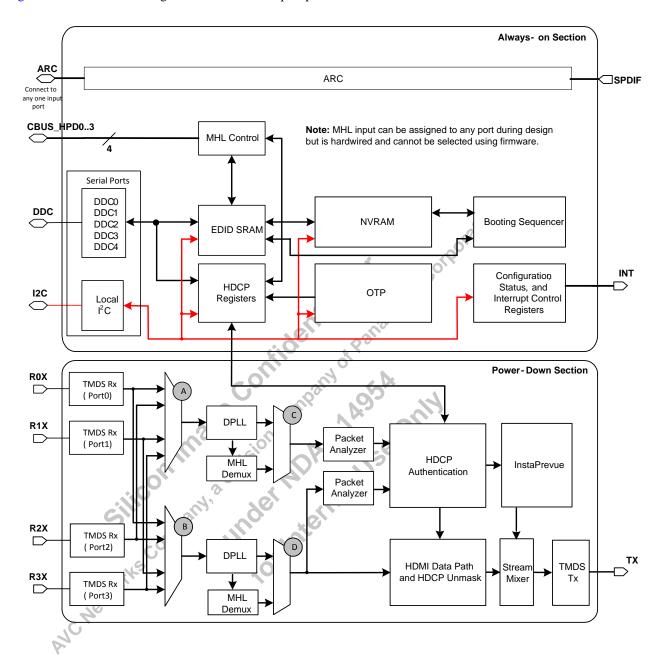

# **Functional Description**

Figure 3 shows the block diagram of the SiI9687A port processor.

Figure 3. Functional Block Diagram

#### **Always-on Section**

The Always-On Section contains the low speed control parts of the HDMI connection, and includes the I<sup>2</sup>C interfaces, internal memory blocks, and the registers that control the blocks of the Power-Down Section.

#### Serial Ports Block

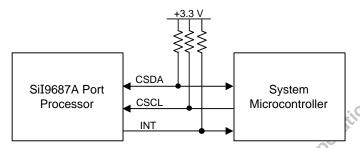

The Serial Ports Block provides six I<sup>2</sup>C serial interfaces: 4 DDC ports to communicate with the HDMI or DVI hosts, 1 VGA DDC port, and one local I<sup>2</sup>C port for initialization and control by a local microcontroller in the display. Each interface is 5 V tolerant. Figure 4 shows the connection of the local I<sup>2</sup>C port to the system microcontroller.

Figure 4. I<sup>2</sup>C Control Mode Configuration

The five DDC interfaces (DDC 0–4) on the SiI9687A port processor are slave interfaces. Each HDMI DDC interface connects to one E-DDC bus and is used to read the integrated EDID and HDCP authentication information. These ports are accessible on the E-DDC bus at device addresses 0xA0 for the EDID and 0x74 for HDCP control. This feature complies with the HDCP 1.4 Specification. The VGA DDC port is only accessible on the E-DDC bus at device address 0xA0 for the EDID.

Refer to the Local I2C section on page 24 for information about the I<sup>2</sup>C addresses and the use of the CI2CA pin.

#### Static RAM Block

The EDID Static RAM (SRAM) Block contains 1280 bytes of RAM. Each port is allocated a 256-byte block for DDC; this allows all ports to be read simultaneously from four different sources connected to the SiI9687A device. A 128-byte block is available for the VGA EDID, 64 bytes are used for the Auto-boot feature, and 64 bytes are reserved. The SRAM can be written to and read from using the local I<sup>2</sup>C interface and it can be read through the DDC interface. The memory can be read without main TV power (VDD33), using 5 V power from the HDMI or VGA connector (RnPWR5V or SBVCC5). See the EDID Memory section on page 23 for information about how the SRAM and NVRAM work together.

#### **NVRAM Block**

The port processor contains 512 bytes of NVRAM, 256 of which is used to store common EDID data used by each of the ports, 128 of which is used for VGA DDC, and 64 of which is used by the Auto-Boot feature. (64 bytes are reserved.) Both the NVRAM EDID data and NVRAM Auto-Boot data should be initialized by software using the local I<sup>2</sup>C bus at least once during the time of manufacture.

#### **HDCP Register Block**

The HDCP Register block controls the necessary logic to decrypt the incoming audio and video data. The decryption process is controlled entirely by the host side microcontroller using a set sequence of register reads and writes through the DDC channel. The decryption process uses pre-programmed HDCP keys and Key Selection Vector (KSV) stored in the on-chip non-volatile memory.

#### **OTP ROM Block**

The OTP ROM Block is programmed at the factory and contains the pre-programmed HDCP keys. System manufacturers do not need to purchase key sets from the Digital Content Protection LLC. All purchasing, programming,

and security for the HDCP keys is handled by Silicon Image. The pre-programmed HDCP keys provide the highest level of security, as keys cannot be read out of the device after they are programmed.

#### **Booting Sequencer**

The Booting Sequencer boots up the required data, such as EDID, initial HPD status, and MHL port selection from NVRAM during power on.

#### Configuration, Status, and Interrupt Control Registers Block

The Configuration, Status, and Interrupt Control Registers block incorporates the registers required for configuring and managing the features of the SiI9687A port processor. These registers are used to perform audio/video/auxiliary format processing, CEA-861E InfoFrame Packet format, and power-down control. The registers are accessible from the local I<sup>2</sup>C port. This block also handles interrupt operations.

#### **MHL Control Block**

The MHL Control Block handles CBUS conversion of DDC signals for the HDCP interface and EDID blocks.

#### **Power-down Section**

The Power-down section contains HDMI high-speed data paths, including the analog TMDS input and output blocks and the digital logic for HDMI data and HDCP processing.

#### **TMDS Receiver Blocks**

The receiver ports, defined as Port 0, Port 1, Port 2, and Port 3 are terminated separately, equalized under the control of the receiver digital block, and controlled by the local  $I^2C$  bus.

# 4:1 Input Multiplexer Blocks

4:1 Input Multiplexer Blocks A and B select one of the four inputs. Multiplexer Block A sequentially selects one of the three inactive inputs and sends its data over the roving pipe to the DPLL block and the MHL demux block. Multiplexer Block B selects the active input and sends its data over the main pipe to be processed.

#### **MHL Demultiplexer Blocks**

If the signal received from the DPLL block only appears in one of the three lanes, the input is an MHL signal. The Demultiplexer block distributes the single-lane RGB serial data blocks over the three parallel RGB lanes of video data.

#### 2:1 HDMI/MHL Multiplexer Blocks

2:1 HDMI/MHL Multiplexer Blocks C and D select either the HDMI from the DPLL block or the MHL converted to HDMI by the MHL Demultiplexer. Block C transfers data from the roving pipe, and block D transfers data from the main pipe.

#### **Packet Analyzer Blocks**

The packet analyzer blocks extract the control signals from the HDMI control packets that are needed to control the HDCP decryption process in the main and the roving pipe. HDCP decryption is controlled by register information.

#### **HDCP Authentication Block**

The active receiver port switched to the main pipe is permanently connected to its HDCP decryption block. The remaining three ports share the roving pipe. Each of the decryption blocks are sequentially switched to its input port for a period long enough to get the control information from the HDMI packets needed for the pre-authentication process. There is a small probability of missing important information in the roving process because of the unpredictable

occurrence of control packets. The missed information is detected and leads to a full re-authentication of the corresponding HDCP path.

#### MP and RP HDMI Receive Data Path and HDCP Unmask Blocks

HDMI data from the Main Pipe (MP) and Roving Pipe (RP) are sent to and processed by the respective HDMI Receive Data Path and HDCP Unmask blocks. The appropriate decryption key for the main port and the input port currently connected to the roving pipe is applied to the XOR mask in these blocks to descramble the video, audio, and auxiliary packets.

#### InstaPrevue Block

The InstaPrevue block merges downscaled images from the roving pipe into the preview positions of main image coming from the main pipe. DeepColor processing, color space conversion, pixel repetition, interleaving, and 3D processing (for 720p and 1080p FramePacking only) are handled properly by the InstaPrevue core. The downscaled image is converted to match the format of the main pipe.

#### **AV Mute Block**

The AV mute block controls audio and video mute, using two methods. Software mute is controlled by register settings. When hardware mute is enabled, audio and video are automatically muted and unmuted if an ECC error occurs.

#### **TMDS Transmitter Block**

The transmitter block delivers an HDMI content stream, based on the content of the original stream from the selected source. Internal source termination eliminates the need to use external R-C components for signal shaping. The internal source termination can be disabled.

#### **ARC Block**

S/PDIF data r. signal. The block embe of the HDMI connector. The Audio Return Channel (ARC) block allows digital S/PDIF data received from the sink device to be transmitted in the direction opposite to the TMDS input port signal. The block embeds the audio data, in single mode format, in the same lines connected to the Utility pin of the HDMI connector.

# **Electrical Specifications**

#### **Absolute Maximum Conditions**

**Table 1. Absolute Maximum Conditions**

| Symbol         | Parameter                                 | Min  | Тур | Max         | Unit | Note |

|----------------|-------------------------------------------|------|-----|-------------|------|------|

| VDD33          | Supply voltage                            | -0.3 | _   | 4.0         | V    | 1, 2 |

| SBVCC5         | Supply voltage                            | -0.3 | _   | 5.7         | V    | 1, 2 |

| RnPWR5V        | 5V input from power pin of HDMI connector | -0.3 | _   | 5.7         | V    | 1, 2 |

| AVDD10         | TMDS receiver core supply voltage         | -0.3 | _   | 1.5         | V    | 1, 2 |

| TAVDD10        | TMDS transmitter core supply voltage      | -0.3 | _   | 1.5         | V    | 1, 2 |

| VDD10          | Digital core supply voltage               | -0.3 | _   | 1.5         | V    | 1, 2 |

| V <sub>I</sub> | Input voltage                             | -0.3 | _   | VDD33 + 0.3 | V    | 1, 2 |

| Vo             | Output voltage                            | -0.3 | _   | VDD33 + 0.3 | V    | 1, 2 |

| T <sub>J</sub> | Junction temperature                      | 0    | _   | 125         | °C   | _    |

| $T_{STG}$      | Storage temperature                       | -65  | _   | 150         | °C   |      |

#### **Notes:**

- Permanent device damage can occur if absolute maximum conditions are exceeded.

- Functional operation should be restricted to the conditions described in the Normal Operating Conditions section below.

**Table 2. ESD Specifications**

| Symbol                                                                      | Parameter                                                                                                                                | Min   | Тур      | Max | Units | Note |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------|----------|-----|-------|------|

| Latch up                                                                    | ESD Latch up                                                                                                                             | ± 200 |          | _   | mA    | 1, 2 |

| HBM                                                                         | Human Body Model                                                                                                                         | ± 4   | _        | _   | kV    | 3    |

| MM                                                                          | Machine Model                                                                                                                            | ± 200 | _        | _   | V     | 4    |

| CDM                                                                         | Charged Device Model                                                                                                                     | ± 1   | . —      | _   | kV    | 5    |

| V <sub>ESD</sub>                                                            | ESD voltage per IEC 61000-4-2 (Contact)                                                                                                  | ± 8   | <u> </u> | _   | kV    | 6    |

|                                                                             | ESD voltage per IEC 61000-4-2 (Air)                                                                                                      | ± 8   | _        | _   | kV    | 6    |

| <ul><li>3. Measured a</li><li>4. Measured a</li><li>5. Measured a</li></ul> | s per JESD78B standard. s per JESD22-A114 standard. s per JESD22-A115 standard, s per JESD22-C101 standard. el tests at HDMI connectors. | Z     |          |     |       |      |

#### Notes:

- 1.

- Measured as per JESD78B standard.

Measured as per JESD22-A114 standard.

Measured as per JESD22-A115 standard.

Measured as per JESD22

System.

- 5.

- System level tests at HDMI connectors.

# **Normal Operating Conditions**

**Table 3. Normal Operating Conditions**

| Symbol             | Parameter                                 | Min  | Тур | Max  | Unit       | Note |

|--------------------|-------------------------------------------|------|-----|------|------------|------|

| VDD33              | Supply voltage                            | 3.14 | 3.3 | 3.46 | V          | _    |

| SBVCC5             | Supply voltage                            | 4.3  | 5.0 | 5.5  | V          | 2, 3 |

| RnPWR5V            | 5V input from power pin of HDMI connector | 4.3  | 5.0 | 5.5  | V          | 2    |

| AVDD10             | TMDS receiver core supply voltage         | 0.95 | 1.0 | 1.05 | V          |      |

| TAVDD10            | TMDS transmitter core supply voltage      | 0.95 | 1.0 | 1.05 | V          |      |

| VDD10              | Digital core supply voltage               | 0.95 | 1.0 | 1.05 | V          |      |

| V <sub>DD33N</sub> | 3.3 V Supply voltage noise                | _    | _   | 100  | $mV_{P-P}$ | 1    |

| $V_{\rm DD10N}$    | 1.0 V Supply voltage noise                | _    | _   | 50   | $mV_{P-P}$ | 1    |

| $T_A$              | Ambient temperature (with power applied)  | 0    | +25 | +70  | °C         | _    |

| Θја                | Ambient thermal resistance (Theta JA)     | _    |     | 28   | °C/W       | 4,5  |

| $\Theta_{ m jc}$   | Junction to case resistance (Theta JC)    | _    | _   | 14.4 | °C/W       | 5    |

#### **Notes:**

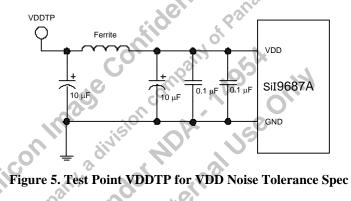

- The supply voltage noise is measured at test point VDDTP shown in Figure 5. The ferrite bead provides filtering of power supply 1. noise. The figure is representative and applies to other VDD pins as well.

- The MHL VBUS voltage requirements may be more stringent than the 5 V power supply requirements for the port processor 2. itself.

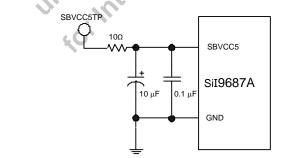

- SBVCC5 Voltage is measured at SBVCC5TP as shown in Figure 3.

- Airflow at 0 m/s. 4.

- The thermal resistance figures are based on a 4-layer PCE 5.

Figure 6. Test Point SBVCC5TP for SBVCC5 Measurement

# **DC Specifications**

Table 4. Digital I/O Specifications

| Symbol               | Parameter                                   | Pin Type <sup>1</sup> | Conditions                                          | Min               | Тур   | Max | Units    | Note |

|----------------------|---------------------------------------------|-----------------------|-----------------------------------------------------|-------------------|-------|-----|----------|------|

| V <sub>IH</sub>      | HIGH-level Input Voltage                    | LVTTL                 | _                                                   | 2.0               | _     | _   | V        | 2    |

| V <sub>IL</sub>      | LOW-level Input Voltage                     | LVTTL                 | _                                                   | _                 | _     | 0.8 | V        | 2    |

| Vth+<br>RESET#       | LOW-to-HIGH threshold<br>RESET # pin        | Schmitt               |                                                     | 2.0               |       |     | V        | _    |

| Vth-<br>RESET#       | HIGH-to-LOW threshold<br>RESET# pin         | Schmitt               |                                                     |                   |       | 0.8 | V        | _    |

| V <sub>TH+DDC</sub>  | LOW-to-HIGH Threshold,<br>DDC Bus           | Schmitt               | _                                                   | 3.0               | _     | _   | V        | 3    |

| V <sub>TH-DDC</sub>  | HIGH-to-LOW Threshold,<br>DDC Bus           | Schmitt               | _                                                   | _                 | _     | 1.5 | V        | 3    |

| V <sub>TH+I2C</sub>  | LOW-to-HIGH Threshold, I <sup>2</sup> C Bus | Schmitt               | _                                                   | 2.0               | _     | _   | V        | _    |

| V <sub>TH-I2C</sub>  | HIGH-to-LOW Threshold, I <sup>2</sup> C Bus | Schmitt               | _                                                   | _                 | - , i | 0.8 | V        | _    |

| V <sub>OH</sub>      | HIGH-level Output Voltage                   | LVTTL                 | $I_{OH} = 4 \text{ mA}$                             | 2.4               | 9     | _   | V        | 4    |

| V <sub>OL</sub>      | LOW-level Output Voltage                    | LVTTL                 | $I_{OL} = -4 \text{ mA}$                            | _                 |       | 0.4 | V        | 4    |

| V <sub>OL_DDC</sub>  | LOW-level Output Voltage                    | Open-<br>drain        | $I_{OL} = -3 \text{ mA}$                            | <del>, 71</del> 0 |       | 0.4 | V        | 3    |

| V <sub>OL_I2C</sub>  | LOW-level Output Voltage                    | Open-<br>drain        | $I_{OL} = -3 \text{ mA}$                            | 50                |       | 0.4 | V        |      |

| $V_{\text{OL\_INT}}$ | LOW-level Output Voltage                    | Open-<br>drain        | $I_{OL} = -3 \text{ mA}$                            | _                 | _     | 0.4 | V        |      |

| $I_{IL}$             | Input Leakage Current                       | LVTTL                 | High<br>Impedance                                   | -10               | _     | 10  | μΑ       |      |

| $I_{OL}$             | Output Leakage Current                      | LVTTL                 | High<br>Impedance                                   | -10               | 3 _   | 10  | μΑ       |      |

| $I_{\mathrm{OD}}$    | 4 mA Digital Output Drive                   | LVTTL                 | $V_{OUT} = 2.4 \text{ V}$ $V_{OUT} = 0.4 \text{ V}$ | 4                 | _     | _   | mA<br>mA | 4 4  |

#### **Notes:**

- Refer to the Pin Descriptions section on page 13 for pin type designations for all package pins.

- Applies to the GPIO, SPDIF, and TPWR\_CI2CA signal pins.

- Applies to the DDC interface.

- Applies to the DDC interface.

Applies to the GPIO and TPWR\_CI2CA signal pins

#### **Table 5. Power Requirements**

| Symbol               | Parameter                                   | Min | Тур | Max  | Unit | Note |

|----------------------|---------------------------------------------|-----|-----|------|------|------|

| I <sub>AVDD10</sub>  | Supply Current for Receiver Analog VDD10    | _   | 100 | 165  | mA   | 1    |

| I <sub>TAVDD10</sub> | Supply Current for Transmitter Analog VDD10 | _   | 10  | 15   | mA   | 1    |

| $I_{VDD33}$          | Supply Current for VDD33                    | _   | 210 | 240  | mA   | 1    |

| I <sub>VDD10</sub>   | Supply Current for Digital VDD10            | _   | 95  | 155  | mA   | 1    |

| $I_{SBVCC5SB}$       | Supply Current for SBVCC5 during standby    | _   | 8   | 13   | mA   | _    |

| $I_{SBVCC5OP}$       | Supply Current for SBVCC5 during operation  | _   | 12  | 15   | mA   | 1    |

| $I_{RnPWR5V}$        | Supply Current for RnPWR5V during operation | _   | _   | 4    | mA   | 1, 2 |

| Total                | Total Power                                 | _   | 960 | 1265 | mW   | 1    |

#### **Notes:**

- Maximum supply currents are measured at maximum operating voltages, with all input and output ports switching at 297 MHz.

- The power provided by  $I_{\mbox{\scriptsize RnPWR5V}}$  is not included in the Total Power row.

#### Table 6. TMDS Input DC Specifications—HDMI Mode

| Symbol            | Parameter                       | Conditions | Min             | Тур | Max              | Units |

|-------------------|---------------------------------|------------|-----------------|-----|------------------|-------|

| $V_{\mathrm{ID}}$ | Differential Mode Input Voltage | _          | 150             | _   | 1200             | mV    |

| V <sub>ICM</sub>  | Common Mode Input Voltage       | _          | AVDD33<br>- 400 | _   | AVDD33<br>- 37.5 | mV    |

#### Table 7. TMDS Input DC Specifications—MHL Mode

| Symbol           | Parameter                             | Conditions | Min    | Тур | Max                                 | Units |

|------------------|---------------------------------------|------------|--------|-----|-------------------------------------|-------|

| $V_{IDC}$        | Single-ended Input DC Voltage         | _          | AVDD33 | _   | AVDD33                              | mV    |

|                  |                                       |            | - 1200 |     | - 300                               |       |

| V <sub>IDF</sub> | Differential Mode Input Swing Voltage | _          | 200    | _   | 1000                                | mV    |

| V <sub>ICM</sub> | Common Mode Input Swing Voltage       | _          | 170    | _   | Min(720,<br>0.85 V <sub>IDF</sub> ) | mV    |

**Table 8. TMDS Output DC Specifications**

| Symbol           | Parameter                              | Conditions             | Min             | Тур | Max             | Units |

|------------------|----------------------------------------|------------------------|-----------------|-----|-----------------|-------|

| $V_{SWING}$      | Single-ended Output Swing Voltage      | $R_{LOAD} = 50 \Omega$ | 400             | 0   | 600             | mV    |

| $V_{\mathrm{H}}$ | Single-ended High-level Output Voltage | _                      | AVDD33 - 200    | GO! | AVDD33 + 10     | mV    |

| $V_{\rm L}$      | Single-ended Low-level Output Voltage  | - 410                  | AVDD33 –<br>700 |     | AVDD33 -<br>400 | mV    |

#### Table 9. Single Mode Audio Return Channel DC Specifications

| Symbol                | Parameter            | Conditions | Min | Тур | Max | Units | Note |

|-----------------------|----------------------|------------|-----|-----|-----|-------|------|

| $V_{el}$              | Operating DC Voltage | 3/1/       | 0   | _   | 5   | V     | _    |

| V <sub>el swing</sub> | Swing Amplitude      | White V    | 400 | 13  | 600 | mV    | _    |

#### **Table 10. CBUS DC Specifications**

| Symbol               | Parameter                        | Conditions         | Min | Тур  | Max  | Units | Note |

|----------------------|----------------------------------|--------------------|-----|------|------|-------|------|

| $V_{IH\_CBUS}$       | High-level Input Voltage         | 6-7                | 1.0 |      |      | V     |      |

| $V_{IL\_CBUS}$       | Low-level Input Voltage          |                    |     |      | 0.6  | V     |      |

| $V_{OH\_CBUS}$       | High-level Output Voltage        | $I_O = 100 \mu A$  | 1.5 |      |      | V     |      |

| $V_{OL\_CBUS}$       | Low-level Output Voltage         | $I_O = 100 \mu A$  |     |      | 0.2  | V     |      |

| $Z_{DSC\_CBUS}$      | Pull-down Resistance – Discovery |                    | 800 | 1000 | 1200 | Ω     |      |

| Z <sub>ON_CBUS</sub> | Pull-down Resistance – Active    | _                  | 90  | 100  | 110  | kΩ    |      |

| I <sub>IL_CBUS</sub> | Input Leakage Current            | High-<br>Impedance | _   | _    | 1    | μΑ    |      |

| $C_{CBUS}$           | Capacitance                      | Power Off          | _   | _    | 30   | pF    | _    |

# **AC Specifications**

#### Table 11. TMDS Input Timing AC Specifications - HDMI Mode

| Symbol                        | Parameter                                 | Conditions | Min  | Тур | Max                                                   | Units     | Note |

|-------------------------------|-------------------------------------------|------------|------|-----|-------------------------------------------------------|-----------|------|

| T <sub>INTRA-</sub> PAIR_SKEW | Input Intra-Pair Skew                     | _          | _    | _   | 0.4                                                   | $T_{BIT}$ |      |

| T <sub>INTER-</sub> PAIR_SKEW | Input Inter-Pair Skew                     | _          |      |     | $\begin{array}{c} 0.2T_{PIXEL} \\ + 1.78 \end{array}$ | ns        |      |

| F <sub>RXC</sub>              | Differential Input Clock Frequency        | _          | 25   | _   | 300                                                   | MHz       |      |

| T <sub>RXC</sub>              | Differential Input Clock Period           | _          | 3.33 |     | 40                                                    | ns        |      |

| T <sub>IJIT</sub>             | Differential Input Clock Jitter Tolerance | 300 MHz    |      |     | 0.3                                                   | $T_{BIT}$ |      |

#### Table 12. TMDS Input Timing AC Specifications – MHL Mode

| Symbol                 | Parameter                          | Conditions | Min   | Тур   | Max                         | Units |

|------------------------|------------------------------------|------------|-------|-------|-----------------------------|-------|

| $T_{SKEW\_DF}$         | Input Differential Intra-Pair Skew |            |       |       | 93                          | ps    |

| $T_{SKEW\_CM}$         | Input Common-mode Intra-Pair Skew  |            |       | _     | 93                          | ps    |

| F <sub>RXC</sub>       | Differential Input Clock Frequency | _          | 25    | - 3   | 75                          | MHz   |

| T <sub>RXC</sub>       | Differential Input Clock Period    | _          | 13.33 | 0     | 40                          | ns    |

| T <sub>CLOCK_JIT</sub> | Common-mode Clock Jitter Tolerance | - ~        | _     | oloo. | $0.3T_{BIT} + 200$          | ps    |

| T <sub>DATA_JIT</sub>  | Differential Data Jitter Tolerance |            | into  | _     | 0.4T <sub>BIT</sub> + 88.88 | ps    |

# Table 13. TMDS Output Timing AC Specifications

| Symbol            | Parameter                            | Conditions | Min  | Тур | Max  | Units     | Note |

|-------------------|--------------------------------------|------------|------|-----|------|-----------|------|

| $T_{TXDPS}$       | Intra-Pair Differential Output Skew  | 4          |      | _   | 0.15 | $T_{BIT}$ | _    |

| $T_{TXRT}$        | Data/Clock Rise Time                 | 20%-80%    | 75   | _   | 144  | ps        | _    |

| $T_{TXFT}$        | Data/Clock Fall Time                 | 20%-80%    | 75   | 4 — | 120  | ps        | _    |

| $F_{TXC}$         | Differential Output Clock Frequency  | -          | 25   | _   | 300  | MHz       | _    |

| T <sub>TXC</sub>  | Differential Output Clock Period     | _          | 3.33 | _   | 40   | ns        | _    |

| T <sub>DUTY</sub> | Differential Output Clock Duty Cycle | AP- 10     | 40%  | _   | 60%  | $T_{TXC}$ | _    |

| T <sub>OJIT</sub> | Differential Output Clock Jitter     |            | _    | _   | 0.25 | $T_{BIT}$ | _    |

# **Table 14. Single Mode Audio Return Channel AC Specifications**

| Symbol              | Parameter                 | Conditions | Min   | Тур | Max  | Units | Note |

|---------------------|---------------------------|------------|-------|-----|------|-------|------|

| T <sub>ASMRT</sub>  | Rise Time                 | 10%-90%    | _     | _   | 60   | ns    | _    |

| T <sub>ASMFT</sub>  | Fall Time                 | 10%–90%    | _     | _   | 60   | ns    | _    |

| $T_{ASMJIT}$        | Jitter Max                | _          | _     | _   | 0.05 | UI*   | _    |

| F <sub>ASMDEV</sub> | Clock Frequency Deviation | _          | -1000 |     | 1000 | ppm   |      |

<sup>\*</sup>Note: Proportional to unit time (UI), according to sample rate. Refer to the S/PDIF specification.

Table 15. S/PDIF Input Port AC Specifications

| Symbol          | Parameter   | Conditions | Min | Тур | Max | Units | Note |

|-----------------|-------------|------------|-----|-----|-----|-------|------|

| $F_{I\_SPDIF}$  | Sample Rate | To ARC     | 32  | _   | 48  | kHz   | _    |

| $T_{I\_SPCYC}$  | Cycle Time  | _          | _   | _   | 1.0 | UI*   | _    |

| $T_{I\_SPDUTY}$ | Duty Cycle  | _          | 90  | _   | 110 | %UI*  | _    |

<sup>\*</sup>Note: Proportional to unit time (UI), according to sample rate. Refer to S/PDIF specification.

#### **Table 16. CBUS AC Specifications**

| Symbol                | Parameter                    | Conditions  | Min | Тур | Max | Units                 |

|-----------------------|------------------------------|-------------|-----|-----|-----|-----------------------|

| T <sub>BIT_CBUS</sub> | Bit Time                     | 1 MHz clock | 0.8 | _   | 1.2 | μs                    |

| $T_{BJIT\_CBUS}$      | Bit-to-Bit Jitter            |             | -1% |     | +1% | T <sub>BIT_CBUS</sub> |

| $T_{DUTY\_CBUS}$      | Duty Cycle of 1 Bit          |             | 40% |     | 60% | T <sub>BIT_CBUS</sub> |

| $T_{R\_CBUS}$         | Rise Time                    | 0.2 V-1.5 V | 5   | _   | 200 | ns                    |

| $T_{F\_CBUS}$         | Fall Time                    | 0.2 V-1.5 V | 5   |     | 200 | ns                    |

| $\Delta T_{RF}$       | Rise to Fall Time Difference | _           | _   | _   | 100 | ns                    |

#### Table 17. I<sup>2</sup>C Timing

| Symbol           | Parameter                        | Condition | Min | Тур | Max      | Unit | Figure |

|------------------|----------------------------------|-----------|-----|-----|----------|------|--------|

| F <sub>I2C</sub> | I <sup>2</sup> C frequency range | _         | - 9 | (O) | 400      | kHz  | _      |

| $T_{HDDAT}$      | I <sup>2</sup> C data hold time* | 0–400 KHz | 0   |     | <u> </u> | ns   | _      |

<sup>\*</sup>Note: This minimum hold time is required by CSCL and CSDA pins as an I<sup>2</sup>C slave. The 300ns internal delay for CSDA can be enabled by NVRAM configuration

# **Miscellaneous Timing**

**Table 18. Miscellaneous Timing**

| Miscellaneous Timing Table 18. Miscellaneous Timing |                                              |                             |     |     |     |      |          |       |

|-----------------------------------------------------|----------------------------------------------|-----------------------------|-----|-----|-----|------|----------|-------|

| Symbol                                              | Parameter                                    | Condition                   | Min | Тур | Max | Unit | Figure   | Notes |

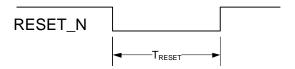

| $T_{RESET}$                                         | RESET_N signal LOW time for valid reset      | ivisi— 10                   | 1   | 13  | _   | ms   | Figure 7 | _     |

| $T_{RESET\_VDD10}$                                  | Time required for RESET_N high before VDD10* | 50% RESET_N<br>to 90% VDD10 | 1   | _   | _   | μs   | Figure 8 | _     |

| T <sub>SBVCC5RT</sub>                               | Rise Time                                    | 10%-90%                     |     | —   | 1   | ms   | _        | _     |

<sup>\*</sup>Note: This time is required due to internal Power-on Reset

# Reset Timings

RESET\_N must be pulled LOW for T<sub>RESET</sub> before accessing registers. This is done by pulling RESET\_N LOW from a HIGH state (shown above) for at least  $T_{\text{RESET}}$ .

Figure 7. RESET\_N Minimum Timing

Figure 8. RESET\_N to VDD10 Timing

# **Pin Descriptions**

# **HDMI and MHL Receiver Port Pins**

| Pin Name | Pin | Type | Dir   | Description                   |

|----------|-----|------|-------|-------------------------------|

| R0X0P    | 53  | TMDS | Input | TMDS input Port 0 data pairs. |

| R0X0N    | 52  |      |       | oto                           |

| R0X1P    | 55  |      |       | of soft                       |

| R0X1N    | 54  |      |       | 60, 00                        |

| R0X2P    | 57  |      |       | TMDS input Port 0 data pairs. |

| R0X2N    | 56  |      |       | 250                           |

| R0XCP    | 51  | TMDS | Input | TMDS input Port 0 clock pair. |

| R0XCN    | 50  |      | Ġ.    | C. A.Y.                       |

| R1X0P    | 63  | TMDS | Input | TMDS input Port 1 data pairs. |

| R1X0N    | 62  |      | C     |                               |

| R1X1P    | 65  |      | 0     | out 180 old                   |

| R1X1N    | 64  |      |       | COMPAN, AMSONIA               |

| R1X2P    | 67  | Mo   | 101   | COMPAN, ABSKONIY              |

| R1X2N    | 66  |      | ijis. | 10h 118                       |

| R1XCP    | 61  | TMDS | Input | TMDS input Port 1 clock pair. |

| R1XCN    | 60  | 4.   |       |                               |

| R2X0P    | 71  | TMDS | Input | TMDS input Port 2 data pairs. |

| R2X0N    | 70  | anil |       |                               |

| R2X1P    | 73  | Co.  | 4     |                               |

| R2X1N    | 72  | 1    | 60    |                               |

| R2X2P    | 75  |      |       |                               |

| R2X2N    | 74  |      |       |                               |

| R2XCP    | 69  | TMDS | Input | TMDS input Port 2 clock pair. |

| R2XCN    | 68  |      |       |                               |

| R3X0P    | 5   | TMDS | Input | TMDS input Port 3 data pairs. |

| R3X0N    | 4   |      |       |                               |

| R3X1P    | 7   | 1    |       |                               |

| R3X1N    | 6   | 1    |       |                               |

| R3X2P    | 9   | 1    |       |                               |

| R3X2N    | 8   | 1    |       |                               |

| R3XCP    | 3   | TMDS | Input | TMDS input Port 3 clock pair. |

| R3XCN    | 2   | 1    |       |                               |

| L        | •   | •    |       |                               |

**Note:** For the port that has been configured as a MHL input, the RnX0P and RnX0N pins carry the MHL signal. All eight TMDS lines require 5.1 ohm series resistors to meet the impedance requirements of both the MHL and HDMI Specifications. HDMI-only ports do not require 5.1  $\Omega$  series resistors on the TMDS lines.

# **Audio Pins**

| Pin Name | Pin | Type   | Dir    | Description                                                                                                                                                             |

|----------|-----|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARC      | 48  | Analog | Output | Audio Return Channel.                                                                                                                                                   |

|          |     |        |        | This pin is used to transmit an IEC60958-1 audio stream, received on the SPDIF_IN input pin, upstream to a compatible source or repeater device, using single-mode ARC. |

| SPDIF_IN | 47  | LVTTL  | Input  | S/PDIF input from the SoC. Pull-down if not used.                                                                                                                       |

# **HDMI Transmitter Port Pins**

| Pin Name | Pin | Type | Dir    | Description                                             |  |

|----------|-----|------|--------|---------------------------------------------------------|--|

| TX0P     | 16  | TMDS | Output | HDMI Transmitter Output Port Data.                      |  |

| TX0N     | 17  |      |        | TMDS Low Voltage Differential Signal output data pairs. |  |

| TX1P     | 14  |      |        |                                                         |  |

| TX1N     | 15  |      |        |                                                         |  |

| TX2P     | 12  |      |        |                                                         |  |

| TX2N     | 13  |      |        |                                                         |  |

| TXCP     | 18  | TMDS | Output | HDMI Transmitter Output Port Clock.                     |  |

| TXCN     | 19  |      |        | TMDS Low Voltage Differential Signal output clock pair. |  |

| 10                    | TMDS Output HDMI Transmitter Output Port Clock.                                     |                                                         |                                                                                                                                                  |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 19                    |                                                                                     | TMDS Low Voltage Differential Signal output clock pair. |                                                                                                                                                  |  |  |  |  |

| System Switching Pins |                                                                                     |                                                         |                                                                                                                                                  |  |  |  |  |

| Pin                   | Туре                                                                                | Dir                                                     | Description                                                                                                                                      |  |  |  |  |

| 39                    | LVTTL                                                                               | Input/                                                  | DDC I <sup>2</sup> C Data for respective port.                                                                                                   |  |  |  |  |

| 35                    | Schmitt                                                                             | Output                                                  | These signals are true open drain, and do not pull to ground when                                                                                |  |  |  |  |

| 31                    | Open-drain                                                                          | -0'                                                     | power is not applied to the device. These pins require an external                                                                               |  |  |  |  |

| 27                    | 5 V tolerant                                                                        | U                                                       | pull-up resistor. Pull-up if not used.                                                                                                           |  |  |  |  |

| 25                    | 76                                                                                  |                                                         |                                                                                                                                                  |  |  |  |  |

| 40                    | LVTTL                                                                               | Input                                                   | DDC I <sup>2</sup> C Clock for respective port.                                                                                                  |  |  |  |  |

| 36                    | Schmitt                                                                             | isio                                                    | These signals are true open drain, and do not pull to ground when                                                                                |  |  |  |  |

| 32                    | 1                                                                                   |                                                         | power is not applied to the device. These pins require an external pull-up resistor. Pull-up if not used.                                        |  |  |  |  |

| 28                    | 5 V tolerant                                                                        |                                                         | pun-up resistor. I un-up it not used.                                                                                                            |  |  |  |  |