# GSV2002

2 In to 2 Out HDMI2.0 Repeater with Audio Extraction/Insertion

August, 2018

#### 1 General Information

#### 1.1 General Information

The GSV2002 is HDMI1.4/2.0 compatible, HDCP 1.4/2.2 supported, configurable 2-in-2-out repeater device. All 2 inputs are identical on receiver capability and all 2 outputs are identical on transmitter capability. GSV2002 is always in 1-in-2-out mode, the distributed video stream can be selected as either one of the 2 inputs.

The HDMI input and output maximum processing pixel clock frequency is 600MHz which means the video resolution can support up to 4kx2k@60Hz 4:4:4 8-bit. The maximum processing audio sample frequency is 192K Hz for non-compression timing. GSV2002 supports HDR10 and Dolby Vision HDR as input and output.

For audio insertion and extraction, the versatile TTL pin bus of GSV2002 can be configured as either input mode or output mode regarding platform requirement. GSV2002 can support up to 8-channel I2S or 2-channel S/PDIF, 3D and multi-stream audio. In TDM mode, each audio pin supports up to 8 channels.

Internal Scaler and Color Space Converter enables the input and output to be timing format independent and capable of long distance transmission.

With powerful HDMI Rx equalizer and Tx pre-emphasis capability, GSV2002 can cascade itself (or GSV2000 series chips) with at least 7 stages for all HDMI 1.3/1.4/2.0 timings.

#### 1.2 Features

## 1.2.1 HDMI Video Input and Output

- Compliant with HDMI2.0b, HDMI1.4b

- Compliant with HDCP2.2/2.3 and HDCP1.4

- Data rate up to 18Gbps

- Programmable HDMI Tx output swing, slew-rate, pre-emphasis

- Adaptive receiver equalization

- AC-coupling capable

- Color Space Converter supports any conversion between different color spaces

- HDR supported (HDR10/HDR12/Dolby Vision/HLG)

- 5V tolerance on DDC/HPD/CEC

- Arbitrary video stream matrix between HDMI Rx and HDMI Tx

## 1.2.2 Audio Input/Output

- SPDIF/I2S/HBR/DSD/TDM Audio Extraction

- SPDIF/I2S/HBR/DSD/TDM Audio Insertion

- Configurable direction for each Audio bus

- Arbitrary audio stream matrix between HDMI Rx/HDMI Tx/Audio bus

#### 1.2.3 Internal Downscaler

Scaler is only used to downscale 4k UHD timings to 2k FHD timings. The horizontal resolution and vertical resolution are both cut in half while frame rate remains the same.

#### 1.2.4 Color Space Converter

Color Space Converter can convert RGB and YCbCr by the following table. It should be noted that YCbCr 422 shares the same color space with YCbCr 444 in internal routing. So any conversion that YCbCr 444 supports, YCbCr 422 also supports it.

Table 1. Color Space Converter Support Table

| From      | To        | To        |

|-----------|-----------|-----------|

| RGB       | YCbCr 444 | YCbCr 420 |

| YCbCr 444 | YCbCr 420 | RGB       |

| YCbCr420  | YCbCr444  | RGB       |

## 1.3 Chip Application Modes

GSV2002 supports 6Gb/s HDMI 2.0 and 1.4 protocol. The 2 video outputs can be fed from any of the 2 video inputs. That means any 1 video input port can drive 2 video outputs at the same time. GSV2002 cannot support RxA-TxA and RxB-TxB mode as chip has only one HDMI Rx Core.

In 1 input to 2 output mode, GSV2002 has the capability to guarantee one video/audio output stream is not disturbed while the other video/audio output stream is switching routing between internal modules.

HDMI video output will not be disturbed when audio insertion is switched between different audio routes.

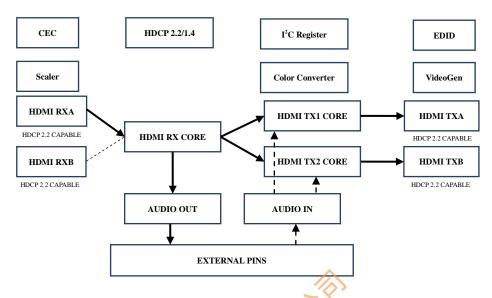

### 1.3.1 Audio Extraction and Video Distribution

GSV2002 has 2 HDMI input ports and 2 HDMI output ports. All of the ports are HDCP 1.4 and HDCP 2.2 capable.

One important purpose of extracting HDMI encrypted stream is to extract audio, process it in audio signal processing chip (DSP/FPGA e.g.). As shown below, TTL audio pins can be configured as output to implement this feature. It should be noted that extracted audio stream is routed from the selected HDMI input to distribute to HDMI outputs.

Limited by the only audio TTL bus, when audio extraction is implemented, audio insertion can not be implemented. So when using audio extraction, both Txs' audio can only be streamed from HDMI Rx rather than from external audio input.

Figure 1. GSV2002 audio extraction diagram

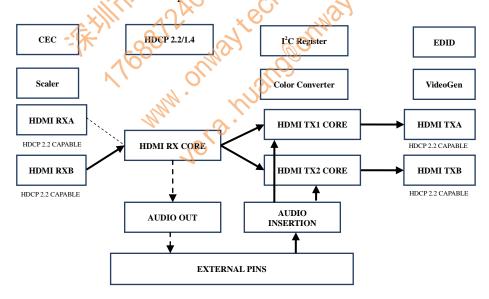

#### 1.3.2 Audio Insertion and Video Distribution

Inserted audio can be routed to any individual Tx or both Tx streams while HDMI video is still routed from HDMI Rx

Limited by the only audio bus, when audio insertion is implemented, audio extraction can not be implemented. In this mode, both Txs audio can be streamed either from HDMI Rx or external audio input.

Figure 2. GSV2002 audio insertion diagram

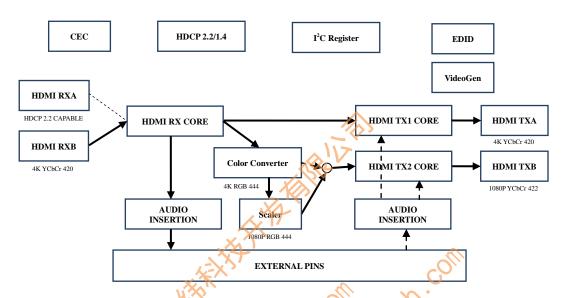

#### 1.3.3 HDMI 2.0 to HDMI 1.4 downscaler

GSV2002 has a built-in scaler and color converter. These blocks enable the chip to do internal video processing for matching HDMI source and sink's capability with a

wider range and better performance. Flexible connection between IPs creates versatile usage modes.

Here is an example of 4K YCbCr 420 (300MHz pixel clock) input, 4K YCbCr 420 (300MHz pixel clock) output and 1080p YCbCr 422 (150MHz pixel clock) output. It should be noted that Tx Core can still do color space conversion (except for YCbCr420) without Color Conversion block. This makes HDMI output flexible in color space.

Figure 3. GSV2002 4K 420-to-1080p 422 diagram

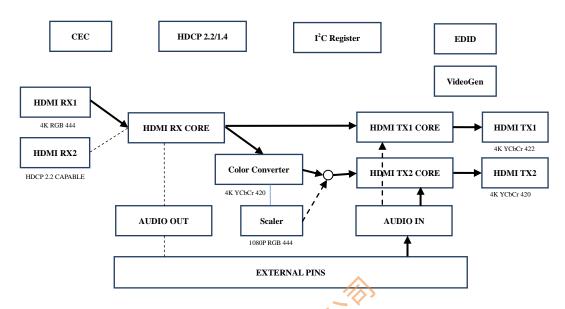

## 1.3.4 HDMI 2.0 YCbCr 420 color space conversion

Here is an example of 4K RGB 444 (600MHz pixel clock) input, 4K YCbCr 422 (600MHz pixel clock) output and 4K YCbCr 420 (300MHz pixel clock) output. It should be noted that Tx Core can still do color space conversion (except for YCbCr420) without Color Conversion block. This makes HDMI output flexible in color space.

Figure 4. GSV2002 4K 444-to-4K 420 diagram

## 1.4 Audio Bus Output Capability

When one group of audio bus is configured as output, I2S and SPDIF are output at the same time. Normal Pin Setting is as below.

Table 2. I2S/SPDIF Audio Extraction

| Pin Name | Alias 📈   | Direction | Description                           |

|----------|-----------|-----------|---------------------------------------|

| AP0      | SDATA[0]  | Output    | 12S Data, default stereo channels     |

| AP1      | SDATA[1]  | Output    | I2S Data, 3/4 channels                |

| AP2      | SDATA[2]  | Output Q  | 12S Data, 5/6 channels                |

| AP3      | SDATA[3]  | Output    | I2S Data, 7/8 channels                |

| AP4      | SPDIF     | Output    | SPDIF channel                         |

| AP5      | LRCLK/WS  | Output    | Fs $(0 = Left, 1 = Right)$            |

| SCLK     | BCLK      | Output    | Fixed to 64Fs                         |

| MCLK     | Sys Clock | Output    | Selected from 128Fs/256Fs/384Fs/512Fs |

For HBR application, SPDIF are also capable of sending out with 4 pins.

Table 3. HBR Audio Extraction in SPDIF

| TWO OF THE THE TWO DAMES WE WANTED TO |          |           |                             |  |

|---------------------------------------|----------|-----------|-----------------------------|--|

| Pin Name                              | Alias    | Direction | Description                 |  |

| AP0                                   | SPDIF[0] | Output    | SPDIF Data[0], 1/2 channels |  |

| AP1                                   | SPDIF[1] | Output    | SPDIF Data[1], 3/4 channels |  |

| AP2                                   | SPDIF[2] | Output    | SPDIF Data[2], 5/6 channels |  |

| AP3                                   | SPDIF[3] | Output    | SPDIF Data[3], 7/8 channels |  |

| AP4                                   | SPDIF    | Output    | SPDIF channel, 1/2 channels |  |

## 1.5 Audio Bus Input Capability

When Audio Bus is set to Input, either I2S or SPDIF can be selected as audio input source. It should be noted that MCLK must be externally fed into GSV chip in I2S

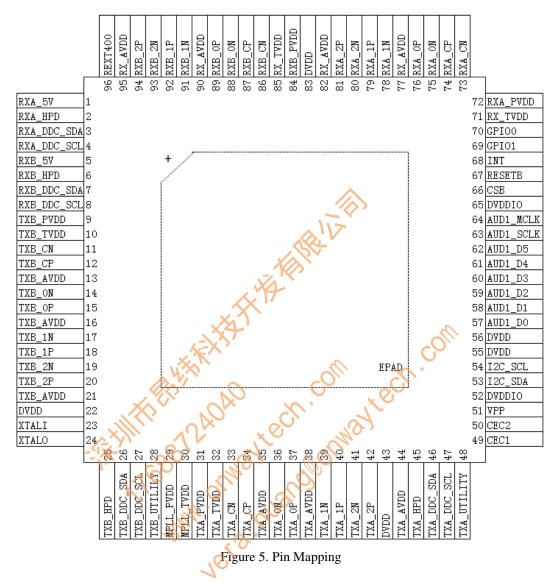

## 2 Pin Description

## 2.1 Pin Diagram

## 2.2 Pin Description

Table 7. Pin Description

| Pin No. | Pin Name    | Direction | Description                                                                                                                                                                                                    |

|---------|-------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | RXA_5V      | Power     | RXA 5V POWER                                                                                                                                                                                                   |

| 2       | RXA_HPD     | I/O       | RXA 5V tolerance HPD PAD                                                                                                                                                                                       |

| 3       | RXA_DDC_SDA | I/O       | RXA 5V tolerance DDC SDA PAD                                                                                                                                                                                   |

| 4       | RXA_DDC_SCL | I         | RXA 5V tolerance DDC SCL PAD                                                                                                                                                                                   |

| 5       | RXB_5V      | Power     | RXB 5V POWER                                                                                                                                                                                                   |

| 6       | RXB_HPD     | I/O       | RXB 5V tolerance HPD PAD                                                                                                                                                                                       |

| 7       | RXB_DDC_SDA | I/O       | RXB 5V tolerance DDC SDA PAD                                                                                                                                                                                   |

| 8       | RXB_DDC_SCL | I         | RXB 5V tolerance DDC SCL PAD                                                                                                                                                                                   |

| 9       | TXB_PVDD    | Power     | PLL 1.2V voltage power supply for TXB channel<br>When PCB combined with DVDD, TX_PVDD can also be<br>increased to 1.28V~1.32V(typical 1.30V) for compensation of<br>complex system level integrity margin loss |

| 10      | TXB_TVDD    | Power     | Analog 3.3V voltage power supply for TXB channel                                                                                                                                                               |

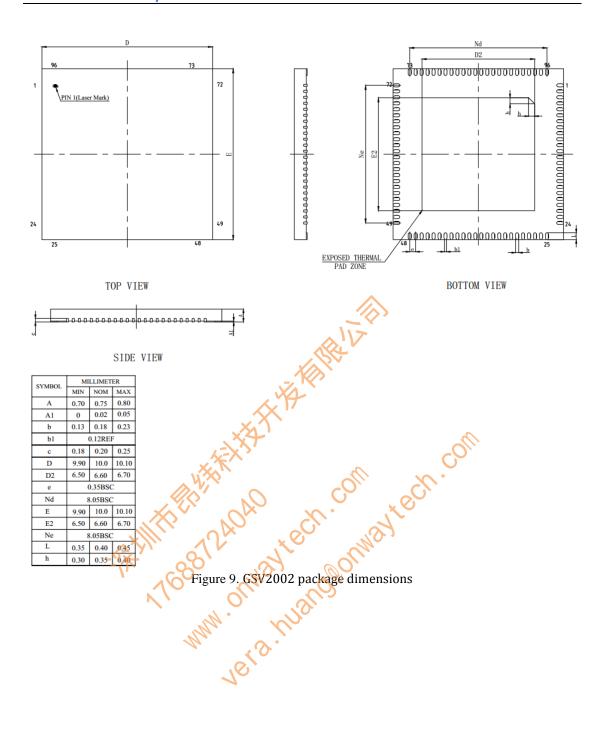

# **5 Ordering Guide**

Table 10. Ordering Infomation

| Part<br>Number. | Temperature<br>Range | Package Description                               | Packing Type |

|-----------------|----------------------|---------------------------------------------------|--------------|

| GSV2002         | -20 ℃ to +85 ℃       | QFN96L, 0.35 mm ball pitch, 10 mm x 10 mm outline | Tray         |

TRAINTHE BANGONIAN TECH. COM VECCO. COM VECC